TSV Process Services

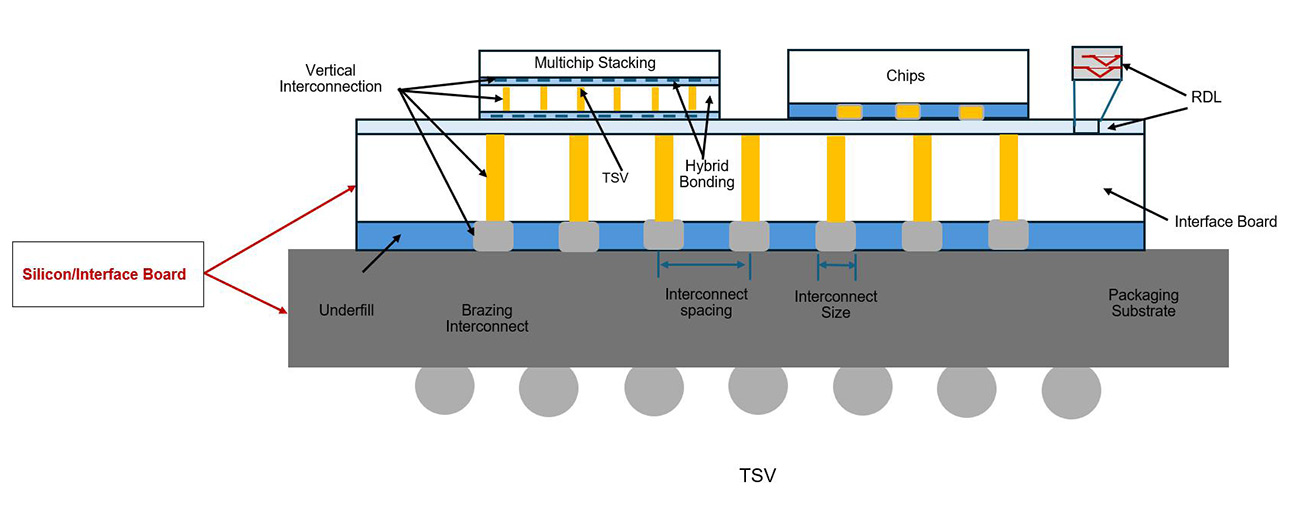

TSV (Through Silicon Via) is an advanced packaging technology that enables the integration of different functional chips by passing silicon channels vertically through the different chips or layers that make up the stack. TSV mainly through the filling of copper and other conductive substances to complete the vertical electrical interconnections of the silicon through-hole, reduce signal delay, reduce capacitance and inductance, to achieve the chip's low-power, high-speed communication, increase the bandwidth and achieve the demand for miniaturisation of device integration.

Previously, most connections between chips were horizontal, and the creation of TSVs made it possible to stack multiple chips vertically. Wire bonding and Flip-Chip bumping provide electrical interconnections to the outside of the die, RDL (re-directed wiring) provides horizontal interconnections inside the die, and TSV provides vertical interconnections inside the wafer.

TSVs are used in three main application directions: backside attachment, 2.5D package, 3D package.

Vertical backside connection. No chip stacking, e.g. ‘simple backside connection’. TSVs are located in the active die and are used to connect to the bond pad on the backside of the wafer.

2.5D package. The die is attached to the silicon interposer and the TSVs are in the interposer.

3D packages. TSVs are located in the active die to enable chip stacking.

Our Processes:

Hole Forming: Hole forming can be done by laser drilling, dry etching, wet etching, and so on.

Deposition of insulating layer: TSV in-hole insulating layer is used to realise the insulation between the silicon substrate and the in-hole transmission channel, preventing leakage and crosstalk between TSV vias.

Deposition of barrier/seed layer: Copper is generally used as the internal metal interconnect material for TSV vias in the 2.5D TSV interlayer process.

Plating Filling: Filling of deep TSV vias is a key technology for 3D integration and is directly related to the electrical performance and reliability of subsequent devices. Materials that can be filled include copper, tungsten, polysilicon, etc.

CMP (Chemical Mechanical Polishing): CMP technology is used to remove silica dielectric, barrier and seed layers from silicon surfaces.

Wafer Thinning: After the wafer surface is flattened, the backside of the wafer is thinned to expose the TSVs.